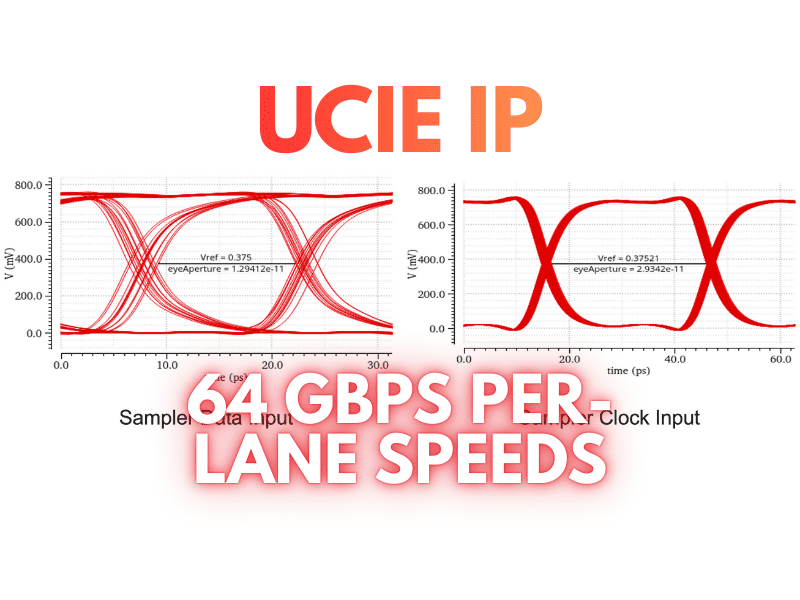

Cadence has taped out a third-generation Universal Chiplet Interconnect Express (UCIe) IP solution supporting data rates of up to 64 Gbps per lane on TSMC’s N3P process. The development reflects continued momentum around chiplet-based architectures as designers push for higher bandwidth and tighter integration at advanced nodes.

For eeNews Europe readers, the update is relevant as UCIe IP increasingly shapes how European engineers approach multi-die integration, particularly for AI accelerators, high-performance computing and data centre platforms where bandwidth density and power efficiency are becoming system-level constraints.

UCIe IP targets higher bandwidth at advanced nodes

According to Cadence, the taped-out UCIe IP is compliant with the UCIe specification and is intended to support scalable die-to-die interconnects at leading-edge process technologies. Moving to TSMC’s N3P node potentially allows higher performance-per-watt compared with earlier implementations, although final system-level gains will depend on packaging, integration choices and workload profiles.

The company positions the solution as part of a broader push to address power, performance and area trade-offs that emerge as designs move to 3nm-class nodes. High-speed die-to-die links are increasingly critical in this context, particularly as monolithic scaling gives way to heterogeneous integration strategies.

Cadence notes that the IP supports multiple protocols, including AXI, CXS, CHI-C2C, PCIe and CXL, which could simplify integration into a range of chiplet-based systems. Such flexibility may be relevant for European system designers working across mixed-vendor ecosystems or targeting reuse across different platforms.

Chiplet connectivity for AI and HPC systems

At 64 Gbps per lane, the UCIe IP is positioned to support high aggregate bandwidth between chiplets, which is a key requirement for AI and HPC workloads. Cadence reports bandwidth density figures that vary depending on packaging approach, indicating that advanced packaging technologies remain a critical factor in realising the full potential of high-speed interconnect IP.

The solution also includes features such as error correction, lane margining and diagnostic support, aimed at improving robustness during bring-up and operation. Cadence states that self-calibrating capabilities may reduce the need for firmware intervention during system initialization, potentially shortening development cycles.

“Cadence has been at the forefront of die-to-die interface solutions since our first tapeout in 2018. Pivoting to UCIe in 2022, we have extensively demonstrated silicon proofs of our Gen 1 and Gen 2 UCIe solutions over the past two years,” said Arif Khan, vice president of marketing in the Silicon Solutions Group at Cadence. “Given the insatiable demand for throughput and efficiency driven by AI and HPC applications, we are proud to make our third-generation UCIe IP—achieving speeds of 64G—available.”

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News